2020. 5. 13. 18:12ㆍSTM32F/코드

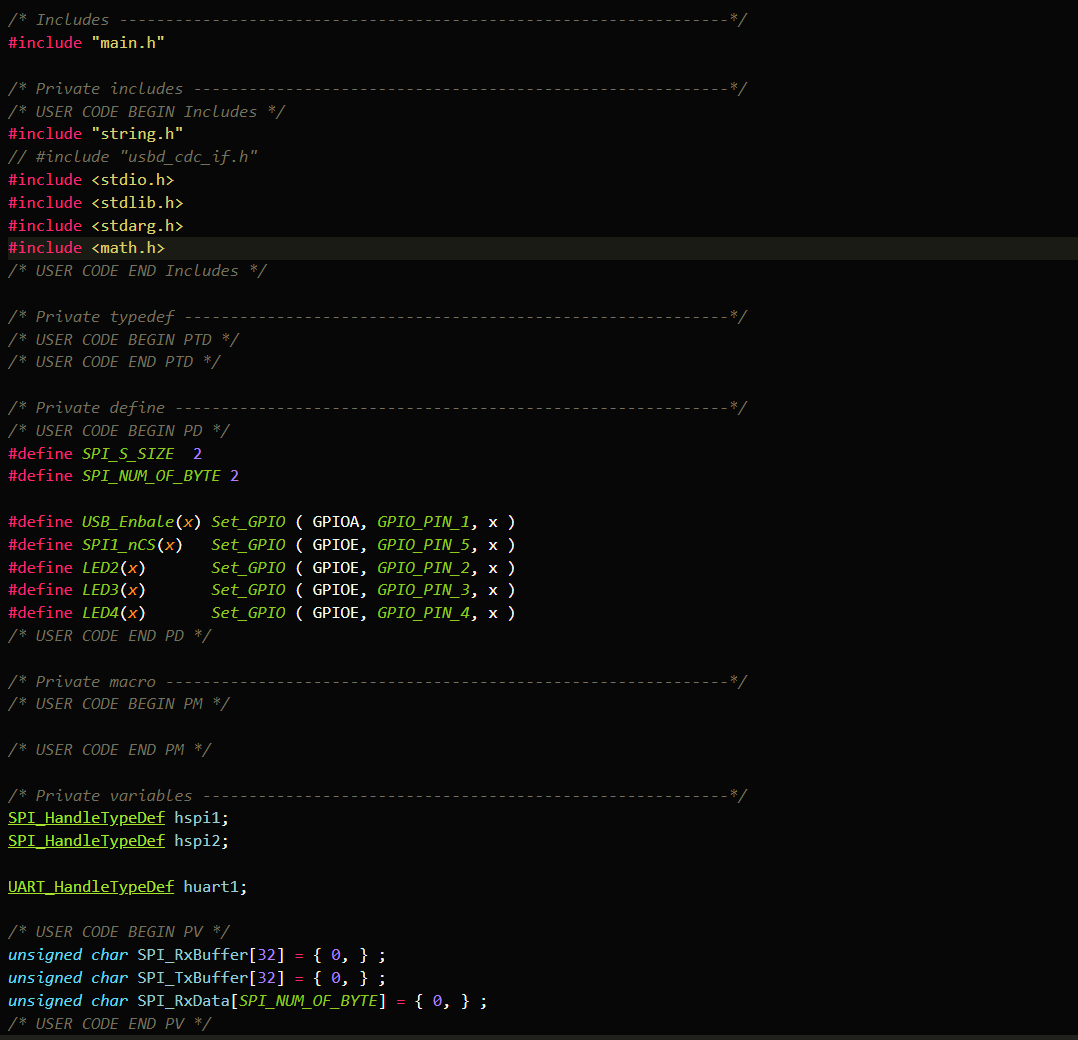

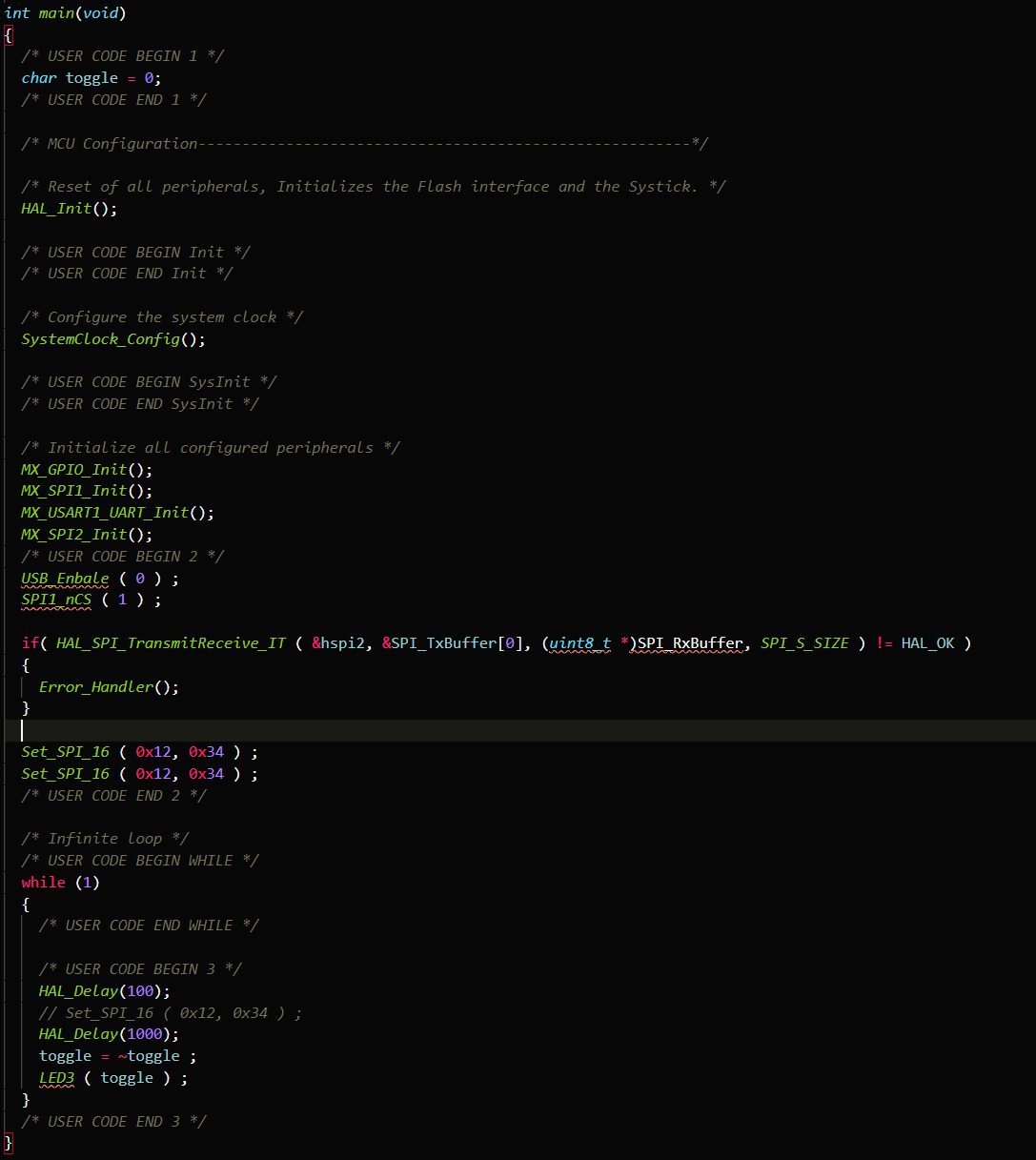

*Clock Paramters - CPOL, CPHA 설정 CPOL - Low, CPHA - 2 Edge 로 설정?? 현재 하나의 MCU 에서 마스터 및 슬레이브 구성 시 Polarity / Phase 동일 하게 설정 하면 엉뚱한 값이 읽힌다???? 그래서 아래와 같이 설정 하면 제대뢰된 값이 읽힌다.. 흠 나중에 원인 팍악 해야됨.... / MISO, MOSI 스코프로 측정 해면 타이밍은 CPOL - Low / CPHA 1Edge로 나온다??? ㅋㅋ, 개인적인 생각이지만 SPI 마스터 / 슬레이브가 같이 타이밍에 동작을 하기 때문에???..ㅋㅋ st 개발자는 알겠지.. 흠..

아니면 마스터 슬레이브 둘다 인터럽트 처리 해야되나?? 이건 해보지 않음..!! 뭐 어째든 이래나 저래나 동작은 되야하는거 같은데.. 이상함..

*다른 실험으로 마스터 SPI Core 를 FPGA ( CPOL - Low / CPHA 1Edge ) 로 구성 하고 했을 때는 슬레이브 CPOL - Low / CPHA 1Edge 로 설정 후 제대로 동작하는걸 확인함..!! 시간이 되면 두개의 MCU 로 다시 한번 해봐야 겠슴..

8비트 이상의 데이터를 보낼경우는 마스터SPI 클럭을 최대한 낮춰서 구성 하면 제대로 동작한다. 24비트 데이터 전송시 약 2MHz 언더 클럭 설정 ( 슬레이브에서 8비트 모드로 사용하고 있기 때문에 마스터에서 8비트 이상의 데이터를 사용하면 spi 클럭을 낮추던 아니면 8비트씩 나눠서 ( 일정 지연시간 ) 주면 동작한다.

이유는 쉽게 8비트 데이터를 받을때마다 RX 인터럽트가 발생되기 때문이다. )

'STM32F > 코드' 카테고리의 다른 글

| RTC + VBAT (0) | 2020.09.04 |

|---|---|

| STM32CubeIDE___SPI_Slave_DMA (0) | 2020.05.18 |

| STM32CubeIDE___SPI Code (0) | 2020.05.04 |